include/rtdm/rtserial.h File Reference

Detailed Description

Real-Time Driver Model for Xenomai, serial device profile header.

- Note:

- Copyright (C) 2005-2007 Jan Kiszka <jan.kiszka@web.de>

Xenomai is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details.

You should have received a copy of the GNU General Public License along with Xenomai; if not, write to the Free Software Foundation, Inc., 59 Temple Place - Suite 330, Boston, MA 02111-1307, USA.

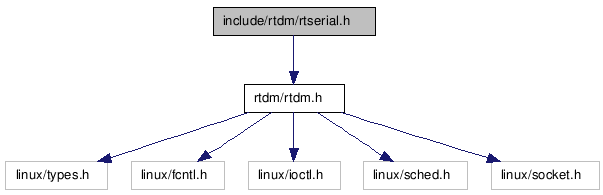

Include dependency graph for rtserial.h:

Go to the source code of this file.

Data Structures | |

| struct | rtser_config |

| Serial device configuration. More... | |

| struct | rtser_status |

| Serial device status. More... | |

| struct | rtser_event |

| Additional information about serial device events. More... | |

RTSER_BREAK_xxx | |

| Break control | |

| #define | RTSER_BREAK_CLR 0x00 |

| Serial device configuration. | |

| #define | RTSER_BREAK_SET 0x01 |

| Serial device configuration. | |

| #define | RTIOC_TYPE_SERIAL RTDM_CLASS_SERIAL |

| Serial device configuration. | |

| typedef struct rtser_config | rtser_config_t |

| Serial device configuration. | |

| typedef struct rtser_status | rtser_status_t |

| Serial device status. | |

| typedef struct rtser_event | rtser_event_t |

| Additional information about serial device events. | |

Defines | |

| #define | RTSER_RTIOC_BREAK_CTL _IOR(RTIOC_TYPE_SERIAL, 0x06, int) |

| Set or clear break on UART output line. | |

RTSER_DEF_BAUD | |

| #define | RTSER_DEF_BAUD 9600 |

RTSER_xxx_PARITY | |

| #define | RTSER_NO_PARITY 0x00 |

| #define | RTSER_ODD_PARITY 0x01 |

| #define | RTSER_EVEN_PARITY 0x03 |

| #define | RTSER_DEF_PARITY RTSER_NO_PARITY |

RTSER_xxx_BITS | |

| #define | RTSER_5_BITS 0x00 |

| #define | RTSER_6_BITS 0x01 |

| #define | RTSER_7_BITS 0x02 |

| #define | RTSER_8_BITS 0x03 |

| #define | RTSER_DEF_BITS RTSER_8_BITS |

RTSER_xxx_STOPB | |

| #define | RTSER_1_STOPB 0x00 |

| valid only in combination with 5 data bits | |

| #define | RTSER_1_5_STOPB 0x01 |

| valid only in combination with 5 data bits | |

| #define | RTSER_2_STOPB 0x01 |

| valid only in combination with 5 data bits | |

| #define | RTSER_DEF_STOPB RTSER_1_STOPB |

| valid only in combination with 5 data bits | |

RTSER_xxx_HAND | |

| #define | RTSER_NO_HAND 0x00 |

| #define | RTSER_RTSCTS_HAND 0x01 |

| #define | RTSER_DEF_HAND RTSER_NO_HAND |

RTSER_FIFO_xxx | |

| #define | RTSER_FIFO_DEPTH_1 0x00 |

| #define | RTSER_FIFO_DEPTH_4 0x40 |

| #define | RTSER_FIFO_DEPTH_8 0x80 |

| #define | RTSER_FIFO_DEPTH_14 0xC0 |

| #define | RTSER_DEF_FIFO_DEPTH RTSER_FIFO_DEPTH_1 |

RTSER_TIMEOUT_xxx | |

| #define | RTSER_TIMEOUT_INFINITE RTDM_TIMEOUT_INFINITE |

| #define | RTSER_TIMEOUT_NONE RTDM_TIMEOUT_NONE |

| #define | RTSER_DEF_TIMEOUT RTDM_TIMEOUT_INFINITE |

RTSER_xxx_TIMESTAMP_HISTORY | |

| #define | RTSER_RX_TIMESTAMP_HISTORY 0x01 |

| #define | RTSER_DEF_TIMESTAMP_HISTORY 0x00 |

RTSER_EVENT_xxx | |

| #define | RTSER_EVENT_RXPEND 0x01 |

| #define | RTSER_EVENT_ERRPEND 0x02 |

| #define | RTSER_EVENT_MODEMHI 0x04 |

| #define | RTSER_EVENT_MODEMLO 0x08 |

| #define | RTSER_DEF_EVENT_MASK 0x00 |

RTSER_SET_xxx | |

| #define | RTSER_SET_BAUD 0x0001 |

| #define | RTSER_SET_PARITY 0x0002 |

| #define | RTSER_SET_DATA_BITS 0x0004 |

| #define | RTSER_SET_STOP_BITS 0x0008 |

| #define | RTSER_SET_HANDSHAKE 0x0010 |

| #define | RTSER_SET_FIFO_DEPTH 0x0020 |

| #define | RTSER_SET_TIMEOUT_RX 0x0100 |

| #define | RTSER_SET_TIMEOUT_TX 0x0200 |

| #define | RTSER_SET_TIMEOUT_EVENT 0x0400 |

| #define | RTSER_SET_TIMESTAMP_HISTORY 0x0800 |

| #define | RTSER_SET_EVENT_MASK 0x1000 |

RTSER_LSR_xxx | |

| #define | RTSER_LSR_DATA 0x01 |

| #define | RTSER_LSR_OVERRUN_ERR 0x02 |

| #define | RTSER_LSR_PARITY_ERR 0x04 |

| #define | RTSER_LSR_FRAMING_ERR 0x08 |

| #define | RTSER_LSR_BREAK_IND 0x10 |

| #define | RTSER_LSR_THR_EMTPY 0x20 |

| #define | RTSER_LSR_TRANSM_EMPTY 0x40 |

| #define | RTSER_LSR_FIFO_ERR 0x80 |

| #define | RTSER_SOFT_OVERRUN_ERR 0x0100 |

RTSER_MSR_xxx | |

| #define | RTSER_MSR_DCTS 0x01 |

| #define | RTSER_MSR_DDSR 0x02 |

| #define | RTSER_MSR_TERI 0x04 |

| #define | RTSER_MSR_DDCD 0x08 |

| #define | RTSER_MSR_CTS 0x10 |

| #define | RTSER_MSR_DSR 0x20 |

| #define | RTSER_MSR_RI 0x40 |

| #define | RTSER_MSR_DCD 0x80 |

RTSER_MCR_xxx | |

| #define | RTSER_MCR_DTR 0x01 |

| #define | RTSER_MCR_RTS 0x02 |

| #define | RTSER_MCR_OUT1 0x04 |

| #define | RTSER_MCR_OUT2 0x08 |

| #define | RTSER_MCR_LOOP 0x10 |

Sub-Classes of RTDM_CLASS_SERIAL | |

| #define | RTDM_SUBCLASS_16550A 0 |

IOCTLs | |

| #define | RTSER_RTIOC_GET_CONFIG _IOR(RTIOC_TYPE_SERIAL, 0x00, struct rtser_config) |

| Get serial device configuration. | |

| #define | RTSER_RTIOC_SET_CONFIG _IOW(RTIOC_TYPE_SERIAL, 0x01, struct rtser_config) |

| Set serial device configuration. | |

| #define | RTSER_RTIOC_GET_STATUS _IOR(RTIOC_TYPE_SERIAL, 0x02, struct rtser_status) |

| Get serial device status. | |

| #define | RTSER_RTIOC_GET_CONTROL _IOR(RTIOC_TYPE_SERIAL, 0x03, int) |

| Get serial device's modem contol register. | |

| #define | RTSER_RTIOC_SET_CONTROL _IOW(RTIOC_TYPE_SERIAL, 0x04, int) |

| Set serial device's modem contol register. | |

| #define | RTSER_RTIOC_WAIT_EVENT _IOR(RTIOC_TYPE_SERIAL, 0x05, struct rtser_event) |

| Wait on serial device events according to previously set mask. | |

1.5.6

1.5.6